PRODUCTS >> RAN Acceleration

OFDM Acceleration IP

Offload computation-intensive OFDM modulation/demodulation workloads to highly optimized hardware with a simple-to-use interface and very high throughput.

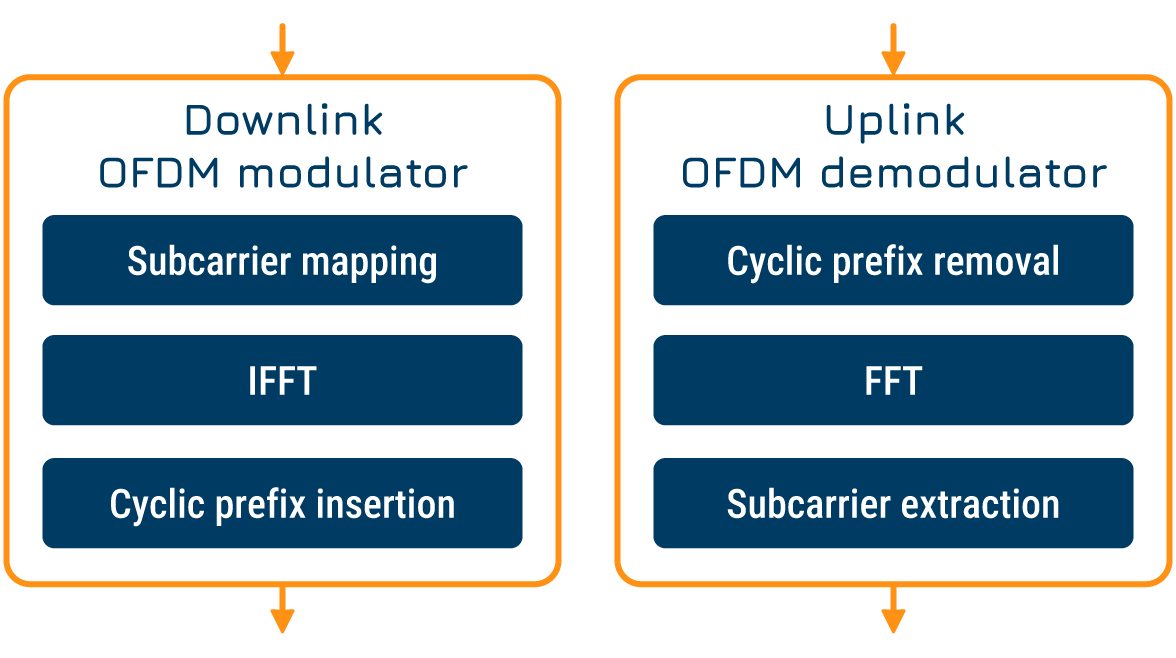

Tannera’s OFDM Acceleration IP is an accelerator solution that implements CP-OFDM modulation/demodulation on an FPGA or ASIC device. The IP supports both the uplink and downlink data path with symmetrical functionalities. At the downlink side, the accelerator performs fully programmable subcarrier mapping (zero padding), IFFT, and cyclic prefix insertion. The uplink datapath includes cyclic prefix removal, FFT, and fully programmable subcarrier extraction (zero stripping). Tannera’s OFDM acceleration IP performs all operations with high throughput and minimal latency, enabling strict constraints imposed by the 5G deployments. This product is fully 5G compatible and customizable to other standards.

High throughput and low latency operation

400 Msym/s operation per HW core,

latency of 2 OFDM symbols

Fully 5G compliant

runtime-reconfigurable FFT size,

multi-antenna operation support,

carrier aggregation support

Deployable to PCIe FPGA cards, SoC FPGA platforms, or ASIC SoCs

Compliant with all numerologies, with no switchover overhead between FR1 and FR2

Fulfills all requirements with respect to SQNR over representative 5G waveforms

In 5G deployments, available automatic CP length selection based on the specifications from TS 38.211, section 5.3.1

Compile-time reconfigurable fixed-point format

Facilitates flexible subcarrier configurations

DPDK/BBDEV-compliant driver for (I)FFT operations, as well as DPDK-based custom driver for full 5G functionality

The OFDM waveform is one of the most commonly used waveforms in the field of wireless communications. It facilitates easy equalization, simple synchronization, and low calculation complexity. Furthermore, beamforming implementations heavily rely on the nature of the OFDM. For transmissions, it provides a well-constrained spectrum with minimal need for time-domain filtering. This is why the OFDM waveform represents one of the fundamentals of wireless technology.

Tannera’s OFDM acceleration IP has all functionalities required by the 3GPP’s Rel. 18 (TS 38.211) standard.

In OFDM, data symbols are transmitted over mutually orthogonal subcarriers by performing an IDFT operation over the transmitted sequence. In order to constrain the spectrum, guard subcarriers filled with zeros are inserted at band edges. A cyclic extension is appended in the time domain to provide orthogonality between consecutive IDFT outputs - called OFDM symbols. Because the IDFT output is, mathematically, a periodic function, a small periodic extension stops the spillover of power from adjacent OFDM symbols due to transients. Periodic extension can be in the form of a prefix, suffix, or both. In 5G NR, a cyclic prefix is used. Tannera’s OFDM acceleration IP facilitates the execution of all of these essential functions in OFDM waveform generation/reception.

The subcarrier mapping (zero padding) enables flexible placement of the data symbols to subcarriers with the insertion of guard bands. The number of zeros inserted before and after the group of active subcarriers is flexible. On the receiver side, a subcarrier extraction component removes guard carriers after the FFT operation. In a PCIe-based solution these components reduce the required PCIe throughput and the number of operations executed in software.

(I)FFT implementation represents a flexible solution with an optimized hardware footprint and efficient utilization of hardware resources. 5G also introduced the concept of variable subcarrier spacings (numerologies) that require runtime switchovers of FFT sizes for constant sampling rates. This use case is fully supported by Tannera's OFDM acceleration IP.

The cyclic prefix insertion and cyclic prefix removal blocks feature a flexible architecture that allows constant or variable CP durations, adjustable to any requirement. The implementation follows the 5G standard, TS 38.211 section 5.3.1, which specifies variable CP duration with a runtime-reconfigurable pattern.